|

|

ENSIKLOPEDIA ELEKTRONIK RADIO DAN KEJURUTERAAN ELEKTRIK Fius elektronik boleh reset

Ensiklopedia elektronik radio dan kejuruteraan elektrik / Perlindungan peralatan daripada operasi kecemasan rangkaian Fius elektronik yang dicadangkan memantau rintangan beban. Ia bukan sahaja mematikannya sekiranya berlaku lebihan beban, tetapi juga memulihkan dirinya kepada mod asal apabila rintangan beban kembali normal. Fius elektronik berkelajuan tinggi yang diterangkan dalam artikel [1] menyambungkan beban secara automatik pada saat dihidupkan jika tiada litar pintas atau beban lampau di dalamnya. Sekiranya berlaku lebihan beban, fius memutuskan sambungan beban. Untuk menghidupkannya semula, anda mesti menekan butang "Mula" fius atau matikan dan hidupkan semula kuasa, yang tidak selalunya mudah. Peranti yang dicadangkan, dibangunkan berdasarkan yang sebelumnya, adalah automatik sepenuhnya. Ia tidak mempunyai badan pentadbir. Peranti menentukan kebolehkhidmatan beban dengan rintangannya. Jika ia lebih besar daripada had yang dibenarkan, beban disambungkan secara automatik ke sumber kuasa. Jika tidak, peranti memutuskan sambungan beban mengikut fungsi fiusnya. Untuk masa yang singkat (kira-kira 10 µs), beban disambungkan secara berkala kepada sumber kuasa melalui perintang pengehad arus. Pada masa ini, fius elektronik mengukur rintangan beban dan, jika ia telah kembali ke had yang dibenarkan, ia sendiri pulih daripada keadaan penutupan beban kecemasan kepada normal. Fius elektronik disambungkan antara bekalan kuasa dan beban. Peranti ini boleh dikendalikan pada voltan 12 hingga 30 V dan arus beban sehingga 20 A. Dua versi peranti telah dibangunkan: dengan menukar wayar negatif atau positif bekalan kuasa beban. Skim varian pertama ditunjukkan dalam rajah. 1, yang kedua - dalam Rajah. 2. Komponen yang menjalankan fungsi yang sama dilabelkan sama.

Peranti (lihat Rajah 1) mempunyai dua litar kawalan beban: awal (pada komparator DA3) dan utama (pada komparator DA4). Rintangan beban diukur apabila ia disambungkan oleh transistor VT1 melalui perintang R2 dan R3. Jika rintangan beban lebih besar daripada ambang operasi yang ditetapkan oleh perintang penalaan R7, transistor pensuisan utama VT2 terbuka, yang menyambungkan beban ke sumber kuasa. Arus beban dalam mod biasa memantau litar utama pada komparator DA4. Jika ia melebihi ambang tindak balas yang ditetapkan oleh perintang perapi R14, transistor pensuisan utama VT2 akan ditutup. Litar awal berdasarkan komparator DA3 mula beroperasi, yang akan membolehkan transistor kesan medan pensuisan utama VT2 dibuka semula apabila rintangan beban kembali ke had yang dibenarkan. Untuk mengawal transistor VT2, seperti dalam peranti sebelumnya [1], flip-flop RS digunakan pada elemen DD1.2 dan DD1.3. Kelebihan flip-flop sedemikian ialah ia membenarkan kehadiran isyarat kawalan aktif secara logik serentak pada kedua-dua input kawalan. Isyarat kawalan yang secara langsung mempengaruhi output yang digunakan [2] mendominasi. Dalam kes kami, keluaran langsung yang digunakan bagi flip-flop RS (pin 3 DD1) dikuasai oleh isyarat aras tinggi yang aktif pada input pemasangan S (pin 1 DD1). Untuk flip-flop RS yang dibuat pada elemen OR-NOT, tahap aktif isyarat langsung keluaran adalah rendah, oleh itu, penyongsang pada elemen DD2 digunakan untuk mengawal transistor VT1.4. Input R RS-flip-flop (pin 8 DD1) disambungkan kepada output DA4 pembanding (pin 9 - pengumpul terbuka). Pada masa power-up dan semasa transien, transistor VT2 ditutup, kerana litar R1C2 menyediakan voltan bekalan melalui penstabil DA1 kepada litar mikro DD1 dan DA2 lebih lewat daripada komparator DA3 dan DA4. Voltan pada input bukan penyongsangan (pin 3) pembanding DA4 adalah lebih besar daripada voltan pada input penyongsangannya (pin 4), jadi transistor keluaran pembanding (pin 2 dan 9) ditutup. Sebaik sahaja kuasa dibekalkan kepada cip DD1, tahap tinggi daripada output DA4 (pin 9) akan menetapkan flip-flop RS kepada keadaan tahap tinggi pada pin 3 DD1. Keluaran penyongsang DD1.4 dan pintu transistor VT2 adalah rendah, jadi ia ditutup. Dalam keadaan ini, transistor VT2 akan sehingga input atas unsur DD1.2 dalam litar menerima nadi peringkat tinggi pendek yang mencetuskan. Ia dijana pada output unsur DD1.1 apabila denyutan aras rendah muncul serentak pada inputnya. Denyutan pencetus diterima pada input atas elemen DD1.1 mengikut litar - denyutan pendek tahap rendah kitaran tugas tinggi, yang dihasilkan oleh penjana pada pemasa DA2, perintang R4, R5 dan kapasitor C4. Tempoh nadi adalah sama dengan R5C4ln2 ~ 25 µs, dan tempoh pengulangannya ialah (R4+2R5)C4ln2 = 2 ms [3]. Selepas memberi tenaga kepada pemasa DA2, nadi pertama pada output 3nya muncul dengan kelewatan (R4+R5)C4ln2 = 2 ms untuk tempoh transien pemasangan awal RS flip-flop DD1.2, DD1.3. Setiap nadi pencetus dari output 3 pemasa DA2 pergi ke input atas elemen DD1.1 mengikut litar dan, pada masa yang sama, melalui penyongsang pada transistor VT3 sudah dalam bentuk nadi peringkat tinggi pendek - ke pintu transistor VT1, yang, membuka, menyambungkan beban ke sumber kuasa melalui perintang R2 dan R3. Mereka bukan sahaja mengehadkan arus beban, tetapi juga membentuk litar untuk mengukur rintangannya: titik sambungan perintang ini disambungkan ke input bukan terbalik (pin 3) pembanding DA3. Litar R4-R6 disambungkan kepada input penyongsangan (pin 8) pembanding ini. Kedudukan perintang perapi R7 menentukan rintangan beban di mana suis DA3 pembanding. Selepas kuasa dihidupkan, transistor VT1 ditutup, jadi voltan pada input bukan penyongsangan DA3 pembanding akan sentiasa lebih besar daripada voltan pada input penyongsangannya, jadi transistor keluaran pembanding (pin 2 dan 9 ) ditutup. Isyarat tunggal pada input bawah elemen DD1.1 memberikan tahap rendah pada outputnya dan, oleh itu, pada input S flip-flop RS, yang dengan itu akan mengekalkan keadaan asalnya. Jika, dengan transistor terbuka VT1, rintangan beban adalah kurang daripada had yang dibenarkan, maka voltan pada input bukan penyongsangan DA3 pembanding akan lebih besar daripada voltan pada input penyongsangannya. Pada output (pin 9) komparator DA3, keadaan yang sama akan kekal semasa transistor VT1 ditutup. Tahap tinggi daripada keluaran komparator DA3, pergi ke input bawah elemen DD1.1, menyekat laluan denyutan pencetus daripada output pemasa DA2 sehingga beban lampau keluaran fius elektronik hilang. Jika, dengan transistor terbuka VT1, rintangan beban lebih besar daripada had yang dibenarkan, maka voltan pada input penyongsangan DA3 pembanding akan lebih besar daripada voltan pada input bukan penyongsangannya. Transistor keluaran komparator DA3 (pin 2 dan 9) terbuka. Pada input elemen DD1.1 akan terdapat pertindihan (dengan anjakan sedikit) dalam masa denyutan peringkat rendah yang singkat. Pada output elemen ini, nadi peringkat tinggi pendek akan dihasilkan, yang akan menukar RS-flip-flop pada input S kepada keadaan dengan tahap rendah pada output. Pada masa ini, sudah ada tahap tinggi pada input R daripada komparator DA4. Tetapi isyarat pada input S mempunyai keutamaan yang lebih tinggi, jadi output pencetus adalah rendah. Akibatnya, isyarat tunggal daripada output penyongsang DD1.4 akan membuka transistor VT2. Jika arus beban kurang daripada had operasi perlindungan, pembanding DA4 akan masuk ke keadaan stabil dengan tahap keluaran yang rendah. Transistor terbuka VT2 menetapkan voltan kecil (pecahan volt) pada input bukan penyongsangan DA3 pembanding, tanpa mengira keadaan transistor VT1. Voltan pada input terbalik DA3 adalah hampir separuh daripada voltan masukan. Memandangkan pin 9 komparator DA3 mempunyai tahap rendah yang stabil, denyutan pencetus daripada output pemasa DA2 melalui elemen DD1.1 menyimpan keadaan semasa flip-flop RS. Jika arus beban melebihi had yang dibenarkan, komparator DA4 bertukar supaya transistor keluarannya ditutup. Isyarat tunggal akan menetapkan tahap tinggi pada output pencetus dan, dengan itu, tahap rendah pada output penyongsang DD1.4, akibatnya transistor VT2 akan menutup dan mematikan beban.

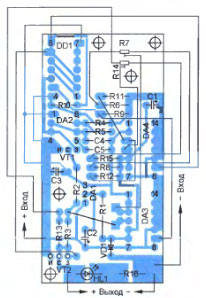

Fius elektronik dengan pensuisan wayar positif berfungsi sama (Rajah 2). Ia dibezakan dengan penggunaan transistor saluran p VT1 dan VT2. Oleh kerana isyarat kawalan mesti digunakan pada gerbang transistor berkenaan dengan sumbernya yang disambungkan ke wayar kuasa positif, ia terbalik. Oleh itu, penyongsang pada elemen DD1.4 dan transistor VT3 tidak digunakan. Pembinaan dan butiran. Fius elektronik dibuat dengan pemasangan permukaan pada papan litar bercetak dengan dimensi 35x70 mm daripada gentian kaca kerajang dua muka. Lukisan papan ditunjukkan dalam rajah. 3 (untuk menukar wayar negatif mengikut rajah dalam Rajah 1) dan dalam rajah. 4 (untuk menukar wayar positif mengikut rajah dalam Rajah 2). Semua bahagian, kecuali transistor VT2, dipasang pada satu sisi papan, kerajang sisi lain digunakan sebagai sink haba untuk transistor VT2 yang dipasang di atasnya.

Pemasa bersepadu KR1006VI1 (DA2) boleh digantikan dengan analog asing NE555N. LED HL1 - sebarang kuasa rendah. Transistor KT361A (VT3) boleh digantikan dengan KT361B-KT361E. Cadangan untuk pemilihan komponen lain adalah sama seperti dalam artikel sebelumnya [1].

Menubuhkan peranti adalah untuk menetapkan ambang pensuisan untuk pembanding DA3 dan DA4 dengan perintang pemangkasan R7 dan R14. Bekalan kuasa makmal disambungkan kepada input, dan ammeter dan reostat disambung secara bersiri, ditetapkan kepada kedudukan rintangan maksimum, disambungkan kepada output. Kepada output komparator DA3 (pin 9) berbanding dengan pin 2, osiloskop disambungkan, diasingkan secara galvani daripada bekalan kuasa. Enjin perintang R7 yang ditala dipasang di bahagian atas mengikut rajah dalam rajah. 1 kedudukan, enjin R14 - ke bahagian bawah dan hidupkan kuasa. Fius mesti menyambungkan beban, yang ditentukan oleh cahaya penunjuk HL1 dan bacaan ammeter. Osiloskop - menunjukkan kehadiran denyutan pendek dengan amplitud kira-kira 9 V. Kurangkan rintangan reostat sehingga ammeter menunjukkan arus perjalanan perlindungan. Selepas itu, peluncur perintang R14 yang ditala digerakkan ke atas mengikut rajah dalam rajah. 1 sehingga beban diputuskan. LED HL1 sepatutnya padam. Kemudian gerakkan perintang pemangkas enjin R7 ke bawah litar (lihat Rajah 1) sehingga hilangnya denyutan pada output komparator DA3. Dengan meningkatkan rintangan beban, pastikan peranti menyambungkannya secara automatik ke sumber kuasa. Penurunan rintangan beban, termasuk kepada litar pintas, akan menyebabkan ia dimatikan dalam kira-kira 10 μs. Sekiranya berlaku lebihan beban semasa dihidupkan, fius elektronik tidak boleh menyambungkan beban. Fius elektronik dipasang mengikut rajah dalam rajah. 2 disediakan dengan cara yang sama, dengan satu-satunya perbezaan ialah peluncur perintang perapi R7 dipraset ke kedudukan bawah mengikut rajah dan digerakkan ke atas, dan peluncur perintang perapi R14 ditetapkan ke kedudukan atas mengikut rajah dan bergerak ke bawah. Parameter denyutan pencetus boleh diubah dengan memilih perintang R4 dan R5. Jika tidak ada keperluan untuk memantau rintangan beban off setiap 2 ms, maka rintangan perintang R4 boleh ditingkatkan sehingga 2 MΩ. Dalam kes ini, tempoh denyutan pencetus akan meningkat secara berkadar. Dengan mengurangkan rintangan perintang R5, adalah wajar untuk mengurangkan tempoh denyutan kepada nilai minimum yang mencukupi di mana peranti menyambungkan beban dengan pasti sepanjang julat voltan bekalan keseluruhan. Adalah wajar untuk mengukur keadaan terbuka transistor VT2 dalam mod litar pintas keluaran pada voltan bekalan maksimum dan mengira tenaga lesap nadi semasa, seperti yang diterangkan dalam artikel sebelumnya [1]. Jika ia melebihi had yang dibenarkan, kurangkan rintangan perintang R5, dan jika peranti berhenti bermula, kemudian kurangkan voltan bekalan maksimum yang dibenarkan atau pilih transistor VT2 yang lebih berkuasa [4, 5]. Adalah mungkin untuk menetapkan fius elektronik sedemikian rupa sehingga komparator DA3 dan DA4 akan bertukar pada rintangan beban yang berbeza. Keperluan untuk ini mungkin timbul apabila menyambungkan beban dengan ciri voltan arus bukan linear. Kesusasteraan

Pengarang: A. Lunaev, Kursk; Terbitan: radioradar.net

Mesin untuk menipis bunga di taman

02.05.2024 Mikroskop Inframerah Lanjutan

02.05.2024 Perangkap udara untuk serangga

01.05.2024

▪ Kawalan laser menggunakan bunyi

▪ bahagian tapak Arus, voltan, pengawal selia kuasa. Pemilihan artikel ▪ artikel Pythagoras. Kata-kata mutiara yang terkenal ▪ pasal hyacinth. Legenda, penanaman, kaedah aplikasi ▪ pasal Menghisap lilin. Resipi dan petua mudah ▪ pasal pengecas antik. Ensiklopedia elektronik radio dan kejuruteraan elektrik

Laman utama | Perpustakaan | artikel | Peta Laman | Ulasan laman web www.diagram.com.ua |

Arabic

Arabic Bengali

Bengali Chinese

Chinese English

English French

French German

German Hebrew

Hebrew Hindi

Hindi Italian

Italian Japanese

Japanese Korean

Korean Malay

Malay Polish

Polish Portuguese

Portuguese Spanish

Spanish Turkish

Turkish Ukrainian

Ukrainian Vietnamese

Vietnamese

Tinggalkan komen anda pada artikel ini:

Tinggalkan komen anda pada artikel ini: